Embedded Middle Hardware LFA series Motionnet<->RS232C Adapter

LFA7

# User's Manual

# 目次

| 1. はじめに 1                       |

|---------------------------------|

| 1.1. 梱包内容2                      |

| 1.2. オーダー情報2                    |

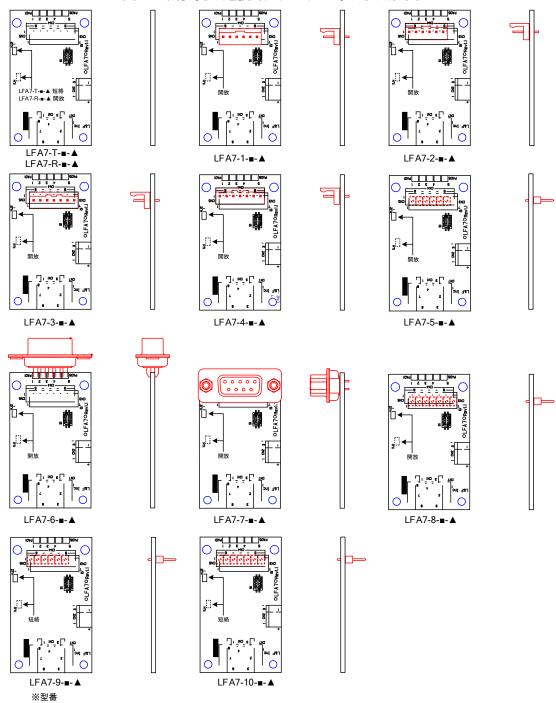

| 1.2.1. 調歩同期通信コネクタオプション実装図3      |

| 1.2.2. 電源コネクタオプション実装図4          |

| 1.2.3. Motionnet 接続コネクタオプション実装図 |

| 2. 基板外形・配置                      |

| 2.1.1. 寸法5                      |

| 2.1.2. 配置6                      |

| 3. 注意事項 7                       |

| 3.1. 安全上のご注意 7                  |

| 3.2. 使用上のご注意 7                  |

| 3.3. その他注意事項 7                  |

| 4. 製品保証                         |

| 4.1. 無償修理8                      |

| 4.2. 有償修理8                      |

| 4.3. 動作を保証できない項目8               |

| 4.4. 免責事項8                      |

| 5. 製品概要                         |

| 6. ハードウェア仕様10                   |

| 6.1. 電気的特性                      |

| 6.2. 一般仕様                       |

| 6.3. 主要部品使用                     |

| 6.4. ブロック図                      |

| 6.5. CPU の設定                    |

| 6.5.1. 端子設定                     |

| 6.5.2. メモリマップ                   |

| 6.5.3. 動作モードの設定18               |

| 6.5.4. クロック設定                   |

| 6.5.5. 割込み設定                    |

| 7. コマンド・レスポンス仕様20               |

| 8. 外部接続仕様23                     |

| 8.1. 調歩同期通信部インターフェース            |

|    | 8.1.1. 電気的インターフェースの選択                    | . 24 |

|----|------------------------------------------|------|

|    | 8.1.2. RS232C DTR 信号によるリセット処理設定ジャンパ(HJ4) | . 24 |

|    | 8.1.3. RS232C シリアル通信信号接続コネクタ 1(CN3)      | . 25 |

|    | 8.1.4. RS232C シリアル通信信号接続コネクタ 2(CN4)      | . 26 |

|    | 8.1.5. RS232C シリアル通信信号接続コネクタ 3(PAD1-9)   | . 27 |

|    | 8.1.6. LVTTL シリアル通信信号接続コネクタ(CN5)         | . 28 |

| 8  | 3.2. モーションネット制御部接続仕様                     | . 29 |

|    | 8.2.1. CN1 シールド処理設定ジャンパ(HJ3)             | . 29 |

|    | 8.2.2. モーションネット接続コネクタ 1(CN1)             | . 30 |

|    | 8.2.3. モーションネット接続コネクタ 2(CN7)             | . 30 |

|    | 8.2.4. CPU と LSI(G9001A)の接続              | . 31 |

|    | 8.2.5. モーションネット制御 LSI(G9001A)の設定端子       |      |

| 8  | 3.3. 電源接続部                               | . 33 |

| 8  | 3.4. CPU デバッグ・プログラム書込み用コネクタ(CN6)         | . 34 |

| 8  | 3.5. 外部からのボードリセット操作                      | . 35 |

|    | 8.5.1. オープンコレクタ・スイッチによるリセット操作            | . 35 |

|    | 8.5.2. RS232C DTR 信号によるリセット操作            | . 35 |

| 9. | インジケーター部                                 | 36   |

|    | 9.1.1. CPU 制御 LED(LED1)                  | . 36 |

|    | 9.1.2. モーションネットステータス LED(LED2,3)         | . 36 |

|    |                                          |      |

# 表目次

| 表 | 1  | オーダー仕様2                                 |

|---|----|-----------------------------------------|

| 表 | 2  | 絶対最大定格10                                |

| 表 | 3  | 推奨動作条件10                                |

| 表 | 4  | 一般仕様                                    |

| 表 | 5  | 端子設定仕様                                  |

| 表 | 6  | CPU メモリマップ(内蔵 ROM 有効拡張モード)17            |

| 表 | 7  | S1 による動作モードの選択                          |

| 表 | 8  | クロック発生回路設定レジスタ19                        |

| 表 | 9  | 割込みレジスタの設定例                             |

| 表 | 10 | デフォルト通信フォーマット20                         |

| 表 | 11 | コマンド・レスポンス仕様21                          |

| 表 | 12 | 調歩同期接続部電気的インターフェース選択24                  |

| 表 | 13 | HJ4 処理仕様24                              |

| 表 | 14 | RS232C シリアル通信信号接続コネクタピンアサイン(CN3)25      |

| 表 | 15 | CN3 実装コネクタ選択仕様25                        |

| 表 | 16 | RS232C シリアル通信信号接続コネクタピンアサイン 2(CN4) 26   |

| 表 | 17 | RS232C シリアル通信信号接続コネクタピンアサイン 3(PAD1-9)27 |

| 表 | 18 | LVTTL シリアル通信信号接続コネクタピンアサイン(CN5)28       |

| 表 | 19 | CN5 実装コネクタ選択仕様28                        |

| 表 | 20 | HJ3 処理仕様29                              |

| 表 | 21 | モーションネット接続コネクタ 1 ピンアサイン(CN1)30          |

| 表 | 22 | モーションネット接続コネクタ 2 ピンアサイン(CN7)30          |

| 表 | 23 | G9001A<->CPU 信号接続仕様                     |

| 表 | 24 | G9001A 固定設定端子設定仕様32                     |

| 表 | 25 | G9001A 設定端子の CPU 端子割付仕様32               |

| 表 | 26 | 電源受電コネクタ(CN2)ピンアサイン33                   |

| 表 | 27 | CN2 実装コネクタ選択仕様33                        |

| 表 | 28 | CPU デバッグ・プログラム書込みコネクタ(CN6)34            |

| 表 | 29 | CPU 制御 LED 制御仕様                         |

| 表 | 30 | G9001A 制御 LED 制御仕様                      |

# 図目次

| 図 1 調歩同期通信オプションコネクタ実装図       3         図 2 電源オプションコネクタ実装図       4         図 3 Motionnet 接続コネクタオプション実装図       4 |

|----------------------------------------------------------------------------------------------------------------|

| 図 3 Motionnet 接続コネクタオプション実装図                                                                                   |

|                                                                                                                |

|                                                                                                                |

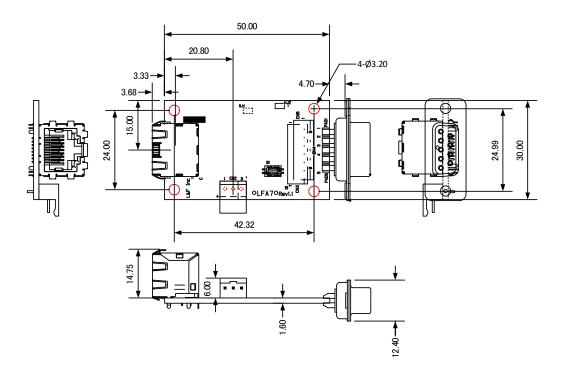

| 図 4 寸法図(基板単体)5                                                                                                 |

| 図 5 寸法図(LFA7-6-2-2)5                                                                                           |

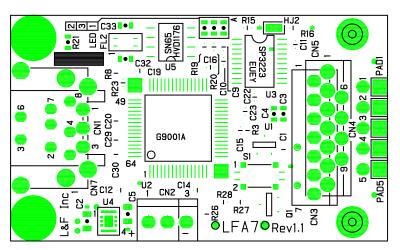

| 図 6 部品面部品配置図6                                                                                                  |

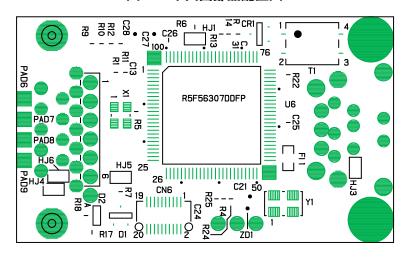

| 図 7 半田面部品配置図6                                                                                                  |

| 図 8 LFA7 ブロック図12                                                                                               |

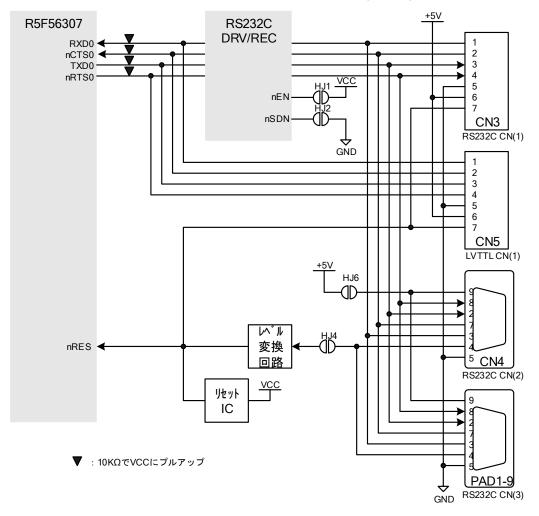

| 図 9 調歩同期インターフェース部接続部23                                                                                         |

| 図 10 PAD1-9 配置図27                                                                                              |

| 図 11 モーションネット部接続図29                                                                                            |

| 図 12 電源部接続図33                                                                                                  |

| 図 13 オープンコレクタ・スイッチによるリセット回路接続図                                                                                 |

| 図 14 RS232C DTR 信号接続図                                                                                          |

|                                                                                                                |

| ※凡例                                                                                                            |

| ● 不定数値の表記は、x で表します。                                                                                            |

| ● 数字の表記 2 進数は B'xxxx、16 進数は H'xxxx、10 進数は xxxx で表します。                                                          |

| ● 記号の表記 ローアクティブの信号には先頭に n を付けています。                                                                             |

| ● 入出力方向は LFA7 側から見た方向を示します。                                                                                    |

| ● 入出力記号は $I=$ 入力、 $O=$ 出力、 $I/O=$ 入出力、 $OC=$ オープンコレクタ、 $PI=$ 電源(入                                              |

| 力 I、PO=電源(出力)を示します。                                                                                            |

| ● デバイスロケーション番号後の(xx)は、端子 No.を示します。                                                                             |

| "大型只之来内状"""(7·20)4月卦(6·1                                                                                       |

# ※本製品主要実装デバイス資料掲載URL

ルネサスエレクトロニクス㈱ http://japan.renesas.com/

トレックス・セミコンダクタ㈱ http://www.torex.co.jp/japanese/

日本パルスモーター株式会社 http://www.pulsemotor.com/

エクサー https://www.exar.com/

#### 1. はじめに

この度は、Motionnet<->RS232C アダプタ LFA7 をお買い上げいただき、

誠にありがとうございます。

本製品は、「ミドルハードウェア」LFA シリーズの Motionnet 対応製品です。

本製品を正しくご使用いただくため、本マニュアル、および、搭載デバイスのマニュアルをご熟読いただけますようお願いいたします。

#### Motionnet とは?

Motionnet は、日本パルスモータ株式会社殿が提唱する

超高速シリアル通信システムです。

このシリアル通信システムは、日本パルスモータ株式会社殿が独自に開発した

5 種類のデバイス: G9001,G9002,G9003, G9103,G9004 をコアにして、

伝送速度 20Mbps のシリアル通信により入出力制御はもちろんのこと、

Motion 制御、高速性を生かした CPU エミュレーション・CPU メッセージ通信 までもが行えるトータル省配線システムです。

くみこみもあい

初めまして、組 込最愛と申します。

皆様の疑問質問にお答えしてまいりますので、どうぞよろしくお 願い致します。

本マニュアルには、LFA7 の仕様や使用方法ついて書かれておりますので、ご活用頂ければ幸いです。

#### 1.1. 梱包内容

基本梱包は下記の通りとなりますので、内容をご確認いただき、万が一不足しておりました場合は、お買い求め販売店、または、弊社サポートまでご連絡下さい。

• LFA7-1-2-3

× 1枚

# 1.2. オーダー情報

LFA7 のオプション品につきまして、下記枝番により部品添付、または、実装対応させていただきます。

型式:LFA7-1-2-3

↑項目番号

表 1 オーダー仕様

| 項目番号 | オプション内容                | オプション番号           | 実装箇所   | 内 容                               |

|------|------------------------|-------------------|--------|-----------------------------------|

|      |                        | T/R               | -      | コネクタなし(T:接続は TTL、R:接続は RS232C)    |

|      |                        | 1                 | CN3    | IL-G-6P(イエローソフト社互換 RS232C)        |

|      |                        | 2                 | CN5    | IL-G-6P (TTL)                     |

|      |                        | 3                 | CN3    | IL-G-7P(RS232C,リセット(オープンコレクタ)入力)  |

|      | 調歩同期通信コネクタ             | 4                 | CN5    | IL-G-7P(TTL,リセット(オープンコレクタ)入力)     |

| 1    | (CN3~5,PAD1~9)         | 5 <sup>**1</sup>  | CN3    | 基板直付けスタックピン(RS232C,6 ピン)          |

|      | 実装仕様                   | 6                 | PAD1-9 | D-sub 9ピンメス横直                     |

|      |                        | 7                 | CN4    | D-sub 9ピンオス縦                      |

|      |                        | 8*1               | CN3    | 基板直付けスタックピン(RS232C, 7 ピン)         |

|      |                        | 9*1               | CN5    | 基板直付けスタックピン(TTL,6 ピン)             |

|      |                        | 10 <sup>* 1</sup> | CN5    | 基板直付けスタックピン(TTL, 7 ピン)            |

|      | 南海コネカカ                 | 0                 | _      | なし                                |

| 2    | 電源コネクタ                 | 1                 | CN2    | IL-G-2P (+5V,GND)                 |

|      | (CN2)実装仕様              | 2                 | CN2    | IL-G-3P(+5V,GND,リセット(オープンコレクタ)入力) |

|      | Mationn at 语/=         | 0                 | _      | なし                                |

| 3    | Motionnet 通信<br>コネクタ仕様 | 1                 | CN1    | DF1B-3P-2.5DS(01)(3P ナイロンコネクタ)    |

|      | コイドン・プログ               | 2                 | CN7    | TM24RSG-5A-88(RJ45 コネクタ)          |

\_\_\_\_ <sup>※1</sup> 半田面実装となります。

### 1.2.1. 調歩同期通信コネクタオプション実装図

#### 図 1 調歩同期通信オプションコネクタ実装図

※全田 ■は電源コネクタオプションで、0~3のいずれか ▲はMotionnetコネクタオプションで、0~2のいずれか ※上図は全て部品面視です。

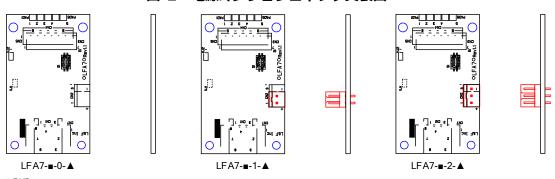

### 1.2.2. 電源コネクタオプション実装図

#### 図 2 電源オプションコネクタ実装図

#### ※型番

- ■は通信コネクタオプションで、T,R,0~10のいずれか

- ▲はMotionnetコネクタオプションで、 $0\sim2$ のいずれか

- ※上図は全て部品面視です。

#### 1.2.3. Motionnet 接続コネクタオプション実装図

#### 図 3 Motionnet 接続コネクタオプション実装図

#### ※型番

- ■は通信コネクタオプションで、T,R,0~10のいずれか ▲は電源コネクタオプションで、0~2のいずれか

# 2. 基板外形・配置

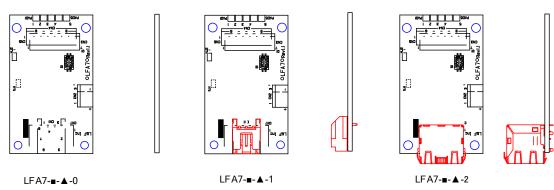

# 2.1.1. 寸法

図 4 寸法図(基板単体)

図 5 寸法図(LFA7-6-2-2)

#### 2.1.2. 配置

#### 図 6 部品面部品配置図

# 図 7 半田面部品配置図

#### 3. 注意事項

本製品は、下記注意事項とともに本マニュアルに記載されている「製品保証」、「免責事項」をご確認いただいたきその内容をご諒承の上ご使用下さい。

#### 3.1. 安全上のご注意

本製品には一般電子機器用(OA機器・通信機器・計測機器・工作機器等)に製造された半導体部品を使用しておりますので、その誤動作や故障が直接生命を脅かしたり、身体・財産等に危害を及ぼす恐れの

ある装置(医療機器・交通機器・燃焼制御・安全装置等)に組み込んで使用しないで 下さい。

また、本製品は半導体製品を使用しております為、外来ノイズやサージ等により誤動作したり故障したりする可能性がありますので、ご使用になる場合は万一誤動作、故障した場合においても生命・身体・財産等が侵害されることのないよう、装置としての安全設計に万全を期されますようお願い致します。

#### 3.2. 使用上のご注意

腐食性ガスや可燃性ガスの雰囲気中でのご使用はお止め下さい。 高湿度環境、水に濡れる恐れのある場所でのご使用はお止め下さい。 温度環境は、本マニュアルに記載された範囲以内でご使用下さい。 基板を金属板等、導電性物質の上に直接置いた状態での通電はお止め下さい。 電源・信号入出力端子に、定格以上の電圧・ノイズを印加しないで下さい。

#### 3.3. その他注意事項

本製品の仕様・本書の内容については、改良の為に予告なく変更する事があります。 本製品・本製品を使用した機器を海外に持ち出される場合は、輸出許可が必要です。 本書に記載されている内容・回路図の著作権は、株式会社エル・アンド・エフが保有 しており、それらを無断で転用・転載・掲載・譲渡・配布することは禁止します。

#### 4. 製品保証

#### 4.1. 無償修理

製品ご購入後1年間は、下記「有償修理」の場合を除き無償で修理致します。(弊社に製品をご返送いただいての修理・交換対応となります。(無償修理を除き、弊社にご送付いただく送料はお客様負担とさせていただきます))

また、保証は製品が日本国内で使用される場合に限り有効とさせていただきます。

#### 4.2. 有償修理

- 1) 製品が購入後1年以上経過しているもの。

- 2) 仕様範囲外でのご使用、物理的/電気的ストレスを加えた等、お客様のお取扱いに起因する故障。

- 3) お客様にて製品を改造(CPUの内容変更も含む) したための故障。

- 4) 火災、地震、水害等の天災による故障。

#### 4.3. 動作を保証できない項目

- 1) 他社製品との接続互換性、相性による不具合。

- 2) 本製品を仕様範囲外の環境でご使用された場合の不具合。

- 3) お客様にて製品を改造したための不具合。

#### 4.4. 免責事項

当製品の故障、不具合、誤動作によって生じた損害等の純粋経済損失につきまして、弊社は一切その責任を負いません。

#### 5. 製品概要

LFA7 は、日本パルスモータ社製Motionnet センターデバイス(G9001A)及び、制御用 CPU を搭載した、小型ユニバーサル基板で、調歩同期方式による簡易通信で、日本パルスモータ社製 3 種類のシリアル通信 LSI(I/O 用ローカルデバイス、パルスコントロール用ローカルデバイス、CPU エミューション用ローカルデバイス)を最大 64 個、通信速度 20Mbps(max)のシリアル通信により、FA 分野に求められている入出力制御が、リモート操作できます。

※モータ制御、CPU エミュレーション、メッセージ通信)入出力制御を行うサイクリック通信では、 4byte のデータ転送を 15.1µsec(max)で常に行い、その間にモータ制御・LSI 制御データなど、 256byte(max)のデータを割り込ませて通信できます。

通信時間は、あらかじめ決められた計算式によって計算可能となっており、FA 分野で必要とされるリアルタイム性を保証しています。

#### 6. ハードウェア仕様

本章では、LFA7のハードウェアに関する機能・性能につき説明します。

CPU のプログラムをお客様にて作成される場合は、本章 6.5CPU の設定の項、ならびに、CPU のハードウェアマニュアルをご熟読の上行って下さい。

(出荷時のプログラム以外に起因する不具合には、対応致しかねますので、プログラム変更を実施されます場合はその点をご留意下さい。)

#### 6.1. 電気的特性

表 2 絶対最大定格

| 項目                | シンボル   | 定 格 値                    | 単位             |

|-------------------|--------|--------------------------|----------------|

| 電源電圧              | +5V    | -0.3~+6.5                | V              |

| Motionnet 部入力電圧範囲 | MNETin | -9∼+14                   | V              |

| RS232C部入力電圧範囲     | RSVin  | ±30                      | V              |

| LVTTL 部入力電圧範囲     | TTLVin | -0.3~+3.6                | V              |

| 保存温度範囲            | Tstg   | -25℃~+85℃(結露なきこと)(カタログ値) | ${\mathcal C}$ |

絶対最大定格を一瞬でも越えた場合、基板上デバイスが永久破壊される場合がありますのでご注意下さい。

表 3 推奨動作条件

| 項目                | シンボル   | 定 格 値                  | 単位         |

|-------------------|--------|------------------------|------------|

| 電源電圧              | +5V    | +4.9~+5.1              | V          |

| Motionnet 部入力電圧範囲 | MNETin | -7∼+12                 | V          |

| RS232C部入力電圧範囲     | RSVin  | ±5~±15                 | V          |

| LVTTL 部入力電圧範囲     | TTLVin | -0.3~+3.3              | V          |

| 動作温度範囲            | TA     | 0℃~+70℃(結露なきこと)(カタログ値) | $^{\circ}$ |

#### 6.2. 一般仕様

表 4 一般仕様

| 項目   | 内容                                    |

|------|---------------------------------------|

| 消費電流 | T.B.DmA (typ)                         |

| 外形寸法 | 30mm(W)×50mm(D)×11mm(H)(オプションコネクタを除く) |

| 質量   | 約 7g(オプションコネクタを除く)                    |

# 6.3. 主要部品使用

| 項目        | 使用デバイス          | 仕様                               |  |  |  |

|-----------|-----------------|----------------------------------|--|--|--|

|           |                 | ・メーカー : ルネサスエレクトロニクス             |  |  |  |

|           |                 | ・クロック : ■メインクロック 14.7456MHz      |  |  |  |

|           |                 | ■システムクロック(ICLK) 最大 88.4736MHz    |  |  |  |

|           |                 | ■周辺モジュールクロック(PCLK) 最大 44.2368MHz |  |  |  |

|           |                 | ・内蔵機能 : ■リセットおよび電原電圧制御: POR,LVD  |  |  |  |

|           |                 | ■内蔵メモリ(ウェイト無)                    |  |  |  |

|           |                 | • FLASH ROM(384Kbyte)            |  |  |  |

| CPU       | R5F56307DDFP#V0 | · SRAM (64KByte)                 |  |  |  |

|           |                 | ■内蔵 E2 データフラッシュ                  |  |  |  |

|           |                 | ・容量: 32Kbyte、                    |  |  |  |

|           |                 | ・プログラム/イレーズ回数:100000 回           |  |  |  |

|           |                 | ■リアルタイムクロック                      |  |  |  |

|           |                 | ■通信機能                            |  |  |  |

|           |                 | I2C,SCI,SPI                      |  |  |  |

|           |                 | ■ウォッチドックタイマ                      |  |  |  |

|           |                 | ■メーカー : トレックス・セミコンダクタ            |  |  |  |

| DC/DC     | XCL202B331BR-G  | ■入力電圧範囲:+4.75~+6VDC              |  |  |  |

| DC/DC     | ACL202B331BR-G  | ■出力電圧:+3.3VDC±2%                 |  |  |  |

|           |                 | ■最大出力電流:400mA                    |  |  |  |

|           |                 | ■メーカー : 日本パルスモーター                |  |  |  |

|           |                 | ■通信仕様:                           |  |  |  |

| Motionnet |                 | 1. 通信速度:2.5M,5M,10M,20Mbps       |  |  |  |

| Host      | G9001A          | 2. 通信符号: NRZ                     |  |  |  |

| Controler | G9001A          | 3. 通信方式:半二重                      |  |  |  |

| Controlei |                 | 4. 通信 I/F: RS485+パルストランス         |  |  |  |

|           |                 | 5. 接続方式:マルチドロップ                  |  |  |  |

|           |                 | 6. ローカルデバイス数 : 最大 64 デバイス        |  |  |  |

|           |                 | ■メーカー:日本パルスモーター                  |  |  |  |

| Pulse     | NDT102E         | ■ 1 次インダクタンス: 1000uH             |  |  |  |

| Trans     | NPT102F         | ■巻線比:N1 対 N2=1 対 1               |  |  |  |

|           |                 | ■耐電圧:AC1500 V rms.1min           |  |  |  |

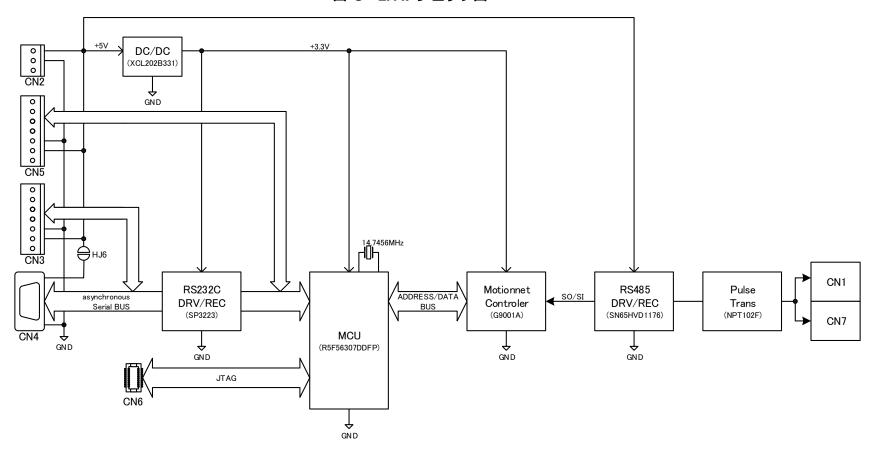

# 6.4. ブロック図

# 図 8 LFA7 ブロック図

#### 6.5. CPU の設定

#### 6.5.1. 端子設定

CPU の各端子は、CPU 内部の設定レジスタにより起動時に下表の状態に設定する必要があります。(設定に誤りがあると本ボードが動作しない場合があります。)

表 5 端子設定仕様

| PIN | 電源クロック    | I/O  | バス    | タイマ                                            | 通信                                               | 割込み     | AD/DA   | 機能・接続                           |

|-----|-----------|------|-------|------------------------------------------------|--------------------------------------------------|---------|---------|---------------------------------|

| NO  | システム      | -, - | . , , |                                                | ~                                                | #37C-17 | ,       |                                 |

| 1   | VREFH     |      |       |                                                |                                                  |         |         | VCCに接続                          |

| 2   | EMLE      |      |       |                                                |                                                  |         |         | JTAG <sup>* 1</sup>             |

| 3   | VREFL     |      |       |                                                |                                                  |         |         | GNDに接続                          |

| 4   |           | РЈЗ  |       | MTIOC3C                                        | CTS6#/RTS6#/CTS0#/                               |         |         | HOST I/F                        |

| 4   |           | L12  |       | MITOCSC                                        | RTS0#/SS6#/SS0#                                  |         |         | UART <sup>※ 1</sup>             |

| 5   | VCL       |      |       |                                                |                                                  |         |         | 0.1uFを接続                        |

| 6   | VBATT     |      |       |                                                |                                                  |         |         | VCCに接続                          |

| 7   | MD/FINED  |      |       |                                                |                                                  |         |         | JTAG <sup>* 1</sup>             |

| 8   | XCIN      |      |       |                                                |                                                  |         |         | 未使用*2                           |

| 9   | XCOUT     |      |       |                                                |                                                  |         |         | 未使用                             |

| 10  | RES#      |      |       |                                                |                                                  |         |         | リセット入力                          |

| 11  | XTAL      | P37  |       |                                                |                                                  |         |         | 14.7456MHz                      |

| 13  | EXTAL     | P36  |       |                                                |                                                  |         |         | を接続                             |

| 12  | VSS       |      |       |                                                |                                                  |         |         | GNDに接続                          |

| 14  | VCC       |      |       |                                                |                                                  |         |         | 電源                              |

| 15  |           | P35  |       |                                                |                                                  | NMI     |         | 未使用*1                           |

| 16  | TRST#     | P34  |       | MTIOCOA/TMCI3/<br>PO12/POE2#                   | SCK6/SCK0                                        | IRQ4    |         | JTAG                            |

| 17  |           | P33  |       | MTIOC0D/TIOCD0/<br>TMRI3/PO11/POE3#            | RXD6/RXD0/SMISO6/<br>SMISO0/SSCL6/SSCL0/<br>CRX0 | IRQ3-DS |         | HOST I/F<br>UART <sup>**1</sup> |

| 18  |           | P32  |       | MTIOCOC/TIOCCO/<br>TMO3/PO10/<br>RTCOUT/RTCIC2 | TXD6/TXD0/SMOSI6/<br>SMOSI0/SSDA6/SSDA0/<br>CTX0 | IRQ2-DS |         | HOST I/F<br>UART**1             |

| 19  | TMS       | P31  |       | MTIOC4D/TMCI2/<br>PO9/RTCIC1                   | CTS1#/RTS1#/SS1#/<br>SSLB0                       | IRQ1-DS |         | JTAG                            |

| 20  | TDI       | P30  |       | MTIOC4B/TMRI3/<br>PO8/RTCIC0/POE8#             | RXD1/SMISO1/SSCL1/<br>MISOB                      | IRQ0-DS |         | JTAG                            |

| 21  | TCK/FINEC | P27  | CS7#  | MTIOC2B/TMCI3/PO7                              | SCK1/RSPCKB                                      |         |         | JTAG                            |

| 22  | TDO       | P26  | CS6#  | MTIOC2A/TMO1/PO6                               | TXD1/CTS3#/RTS3#/<br>SMOSI1/SS3#/SSDA1/<br>MOSIB |         |         | JTAG                            |

| 23  |           | P25  | CS5#  | MTIOC4C/MTCLKB/<br>TIOCA4/PO5                  | RXD3/SMISO3/SSCL3                                |         | ADTRG0# | 未接続<br>(0を出力)                   |

| 24  |           | P24  | CS4#  | MTIOC4A/MTCLKA/<br>TIOCB4/TMRI1/PO4            | SCK3                                             |         |         | 未接続<br>(0を出力)                   |

| 25  |           | P23  |       | MTIOC3D/MTCLKD/<br>TIOCD3/PO3                  | TXD3/CTS0#/RTS0#/<br>SMOSI3/SS0#/SSDA3           |         |         | HOST I/F<br>UART <sup>* 1</sup> |

| 26  |           | P22  |       | MTIOC3B/MTCLKC/<br>TIOCC3/TMO0/PO2             | SCK0                                             |         |         | 未接続<br>(0を出力)                   |

(続く)

# (続き)

| PIN<br>NO | 電源クロック<br>システム | I/O | バス                  | タイマ                                                       | 通信                                                                            | 割込み   | AD/DA   | 機能・接続              |

|-----------|----------------|-----|---------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|-------|---------|--------------------|

| 27        |                | P21 |                     | MTIOC1B/TIOCA3/<br>TMCI0/PO1                              | RXD0/SMISO0/SSCL0                                                             | IRQ9  |         | 未接続<br>(0を出力)      |

| 28        |                | P20 |                     | MTIOC1A/TIOCB3/<br>TMRIO/PO0                              | TXD0/SMOSI0/SSDA0                                                             | IRQ8  |         | 未接続<br>(0を出力)      |

| 29        |                | P17 |                     | MTIOC3A/MTIOC3B/<br>TIOCB0/TCLKD/<br>TMO1/PO15/POE8#      | SCK1/TXD3/SMOSI3/<br>SSDA3/MISOA/SDA2-DS/<br>IETXD                            | IRQ7  | ADTRG#  | 未接続<br>(0を出力)      |

| 30        |                | P16 |                     | MTIOC3C/MTIOC3D/<br>TIOCB1/TCLKC/<br>TMO2/PO14/<br>RTCOUT | TXD1/RXD3/SMOSI1/<br>SMISO3/SSDA1/SSCL3/<br>MOSIA/SCL2-DS/IERXD/<br>USB0_VBUS | IRQ6  | ADTRG0# | 未接続<br>(0を出力)      |

| 31        |                | P15 |                     | MTIOC0B/MTCLKB/<br>TIOCB2/TCLKB/<br>TMCI2/PO13            | RXD1/SCK3/SMISO1/<br>SSCL1/CRX1-DS                                            | IRQ5  |         | 未接続<br>(0を出力)      |

| 32        |                | P14 |                     | MTIOC3A/MTCLKA/<br>TIOCB5/TCLKA/<br>TMRI2/PO15            | CTS1#/RTS1#/SS1#/<br>CTX1/USB0_DPUPE                                          | IRQ4  |         | 未接続<br>(0を出力)      |

| 33        |                | P13 |                     | MTIOC0B/TIOCA5/                                           | TXD2/SMOSI2/SSDA2/                                                            | IRQ3  | ADTRG#  | 未接続                |

|           |                |     |                     | TMO3/PO13                                                 | SDA0[FM+]                                                                     |       |         | (0を出力)             |

| 34        |                | P12 |                     | TMCI1                                                     | RXD2/SMISO2/SSCL2/<br>SCL0[FM+]                                               | IRQ2  |         | 未接続<br>(0を出力)      |

| 35        | VCC_USB        |     |                     |                                                           |                                                                               |       |         | 電源                 |

| 36        |                |     |                     |                                                           | USB0_DM                                                                       |       |         | 未接続                |

| 37        |                |     |                     |                                                           | USB0_DP                                                                       |       |         | 未接続                |

| 38        | VSS_USB        |     |                     |                                                           |                                                                               |       |         | 電源                 |

| 39        |                | P55 | WAIT#               | MTIOC4D/TMO3                                              | CRX1                                                                          | IRQ10 |         | BUS                |

| 40        |                | P54 | ALE                 | MTIOC4B/TMCI1                                             | CTS2#/RTS2#/SS2#/<br>CTX1                                                     |       |         | 未接続<br>(0を出力)      |

| 41        |                | P53 | BCLK                |                                                           |                                                                               |       |         | BCLK出力<br>禁止に設定    |

| 42        |                | P52 | RD#                 |                                                           | RXD2/SMISO2/SSCL2/<br>SSLB3                                                   |       |         | BUS <sup>* 1</sup> |

| 43        |                | P51 | WR1#/BC1#<br>/WAIT# |                                                           | SCK2/SSLB2                                                                    |       |         | 未接続<br>(0を出力)      |

| 44        |                | P50 | WR0#/WR#            |                                                           | TXD2/SMOSI2/SSDA2/<br>SSLB1                                                   |       |         | BUS <sup>* 1</sup> |

| 45        |                | PC7 | A23/CS0#            | MTIOC3A/MTCLKB/<br>TIOCB6/TMO2/PO31                       | TXD8/SMOSI8/SSDA8/<br>MISOA                                                   | IRQ14 |         | 未接続※1              |

| 46        |                | PC6 | A22/CS1#            | MTIOC3C/MTCLKA/<br>TIOCA6/TMCI2/PO30                      | RXD8/SMISO8/SSCL8/<br>MOSIA                                                   | IRQ13 |         | BUS <sup>* 1</sup> |

| 47        |                | PC5 | A21/CS2#/<br>WAIT#  | MTIOC3B/MTCLKD/<br>TIOCD6/TCLKF/<br>TMRI2/PO29            | SCK8/RSPCKA                                                                   |       |         | 未接続<br>(0を出力)      |

| 48        |                | PC4 | A20/CS3#            | MTIOC3D/MTCLKC/<br>TIOCC6/TCLKE/<br>TMCI1/PO25/POE0#      | SCK5/CTS8#/RTS8#/<br>SS8#/SSLA0                                               |       |         | 未接続<br>(0を出力)      |

| 49        |                | PC3 | A19                 | MTIOC4D/TCLKB/                                            | TXD5/SMOSI5/SSDA5/<br>IETXD                                                   |       |         | 未接続<br>(0を出力)      |

| 50        |                | PC2 | A18                 | MTIOC4B/TCLKA/<br>PO21                                    | RXD5/SMISO5/SSCL5/<br>SSLA3/IERXD                                             |       |         | 未接続<br>(0を出力)      |

(続く)

# (続き)

| PIN<br>NO | 電源クロック<br>システム | I/O | バス               | タイマ                                                  | 通信                            | 割込み      | AD/DA | 機能・接続              |

|-----------|----------------|-----|------------------|------------------------------------------------------|-------------------------------|----------|-------|--------------------|

| 51        |                | PC1 | A17              | MTIOC3A/TCLKD/<br>PO18                               | SCK5/SSLA2                    | IRQ12    |       | IRQ <sup>**1</sup> |

| 52        |                | PC0 | A16              | MTIOC3C/TCLKC/<br>PO17                               | CTS5#/RTS5#/SS5#/<br>SSLA1    | IRQ14    |       | 未接続<br>(0を出力)      |

| 53        |                | PB7 | A15              | MTIOC3B/TIOCB5/<br>PO31                              | TXD9/SMOSI9/SSDA9             |          |       | 未接続<br>(0を出力)      |

| 54        |                | PB6 | A14              | MTIOC3D/TIOCA5/<br>PO30                              | RXD9/SMISO9/SSCL9             |          |       | 未接続<br>(0を出力)      |

| 55        |                | PB5 | A13              | MTIOC2A/MTIOC1B/<br>TIOCB4/TMRI1/<br>PO29/POE1#      | SCK9                          |          |       | 未接続<br>(0を出力)      |

| 56        |                | PB4 | A12              | TIOCA4/PO28                                          | CTS9#/RTS9#/SS9#              |          |       | 未接続<br>(0を出力)      |

| 57        |                | PB3 | A11              | MTIOC0A/MTIOC4A/<br>TIOCD3/TCLKD/<br>TMO0/PO27/POE3# | SCK6                          |          |       | 未接続<br>(0を出力)      |

| 58        |                | PB2 | A10              | TIOCC3/TCLKC/<br>PO26                                | CTS6#/RTS6#/SS6#              |          |       | 未接続<br>(0を出力)      |

| 59        |                | PB1 | A9               | MTIOC0C/MTIOC4C/<br>TIOCB3/TMCI0/PO25                | TXD6/SMOSI6/SSDA6             | IRQ4-DS  |       | 未接続<br>(0を出力)      |

| 60        | VCC            |     | 1                |                                                      |                               | <u> </u> |       | 電源                 |

| 61        |                | PB0 | A8               | MTIC5W/TIOCA3/<br>PO24                               | RXD6/SMISO6/SSCL6/<br>RSPCKA  | IRQ12    |       | BUS                |

| 62        | VSS            |     |                  |                                                      |                               |          |       | 電源                 |

| 63        |                | PA7 | A7               | TIOCB2/PO23                                          | MISOA                         |          |       | BUS                |

| 64        |                | PA6 | A6               | MTIC5V/MTCLKB/<br>TIOCA2/TMCI3/<br>PO22/POE2#        | CTS5#/RTS5#/SS5#/<br>MOSIA    |          |       | BUS                |

| 65        |                | PA5 | A5               | TIOCB1/PO21                                          | RSPCKA                        |          |       | BUS                |

| 66        |                | PA4 | A4               | MTIC5U/MTCLKA/<br>TIOCA1/TMRIO/<br>PO20              | TXD5/SMOSI5/SSDA5/<br>SSLA0   | IRQ5-DS  |       | BUS                |

| 67        |                | PA3 | A3               | MTIOCOD/MTCLKD/<br>TIOCD0/TCLKB/<br>PO19             | RXD5/SMISO5/SSCL5             | IRQ6-DS  |       | BUS                |

| 68        |                | PA2 | A2               | PO18                                                 | RXD5/SMISO5/SSCL5/<br>SSLA3   |          |       | BUS                |

| 69        |                | PA1 | A1               | MTIOC0B/MTCLKC/<br>TIOCB0/PO17                       | SCK5/SSLA2                    | IRQ11    |       | BUS                |

| 70        |                | PA0 | A0/BC0#          | MTIOC4A/TIOCA0/<br>PO16                              | SSLA1                         |          |       | 未接続<br>(0を出力)      |

| 71        |                | PE7 | D15<br>[A15/D15] | TIOCB11                                              | MISOB                         | IRQ7     | AN5   | BUS                |

| 72        |                | PE6 | D14<br>[A14/D14] | TIOCA11                                              | MOSIB                         | IRQ6     | AN4   | BUS                |

| 73        |                | PE5 | D13<br>[A13/D13] | MTIOC4C/MTIOC2B/<br>TIOCB10                          | RSPCKB                        | IRQ5     | AN3   | BUS                |

| 74        |                | PE4 | D12<br>[A12/D12] | MTIOC4D/MTIOC1A/<br>TIOCA10/PO28                     | SSLB0                         |          | AN2   | BUS                |

| 75        |                | PE3 | D11<br>[A11/D11] | MTIOC4B/TIOCB9/<br>PO26/POE8#                        | CTS12#/RTS12#/SS12#/<br>MISOB |          | AN1   | BUS                |

(続く)

#### (続き)

| PIN<br>NO | 電源クロック<br>システム | I/O | バス               | タイマ                      | 通信                                                      | 割込み          | AD/DA   | 機能・接続                         |

|-----------|----------------|-----|------------------|--------------------------|---------------------------------------------------------|--------------|---------|-------------------------------|

| 76        |                | PE2 | D10<br>[A10/D10] | MTIOC4A/TIOCA9/<br>PO23  | RXD12/SMISO12/<br>SSCL12/RXDX12/SSLB3/<br>MOSIB         | IRQ7-DS      | AN0     | BUS                           |

| 77        |                | PE1 | D9<br>[A9/D9]    | MTIOC4C/TIOCD9/<br>PO18  | TXD12/SMOSI12/<br>SSDA12/TXDX12/<br>SIOX12/SSLB2/RSPCKB |              | ANEX1   | BUS                           |

| 78        |                | PE0 | D8<br>[A8/D8]    | TIOCC9                   | SCK12/SSLB1                                             |              | ANEX0   | BUS                           |

| 79        |                | PD7 | D7<br>[A7/D7]    | MTIC5U/POE0#             | SSLC3                                                   | IRQ7         | AN7     | BUS                           |

| 80        |                | PD6 | D6[A6/D6]        | MTIC5V/POE1#             | SSLC2                                                   | IRQ6         | AN6     | BUS                           |

| 81        |                | PD5 | D5[A5/D5]        | MTIC5W/POE2#             | SSLC1                                                   | IRQ5         | AN013   | BUS                           |

| 82        |                | PD4 | D4[A4/D4]        | POE3#                    | SSLC0                                                   | IRQ4         | AN012   | BUS                           |

| 83        |                | PD3 | D3[A3/D3]        | TIOCB8/TCLKH/<br>POE8#   |                                                         | IRQ3         | AN011   | BUS                           |

| 84        |                | PD2 | D2[A2/D2]        | MTIOC4D/TIOCA8           |                                                         | IRQ2         | AN010   | BUS                           |

| 85        |                | PD1 | D1[A1/D1]        | MTIOC4B/TIOCB7/<br>TCLKG |                                                         | IRQ1         | AN009   | BUS                           |

| 86        |                | PD0 | D0[A0/D0]        | TIOCA7                   |                                                         | IRQ0         | AN008   | BUS                           |

| 87        |                | P47 |                  |                          |                                                         | IRQ15-<br>DS | AN007   | 未接続<br>(0を出力)                 |

| 88        |                | P46 |                  |                          |                                                         | IRQ14-<br>DS | AN006   | 未接続<br>(0を出力)                 |

| 89        |                | P45 |                  |                          |                                                         | IRQ13-<br>DS | AN005   | 未接続<br>(0を出力)                 |

| 90        |                | P44 |                  |                          |                                                         | IRQ12-<br>DS | AN004   | 未接続<br>(0を出力)                 |

| 91        |                | P43 |                  |                          |                                                         | IRQ11-<br>DS | AN003   | 未接続<br>(0を出力)                 |

| 92        |                | P42 |                  |                          |                                                         | IRQ10-<br>DS | AN002   | 未接続<br>(0を出力)                 |

| 93        |                | P41 |                  |                          |                                                         | IRQ9-DS      | AN001   | MNET <sup>※1</sup><br>速度設定(1) |

| 95        |                | P40 |                  |                          |                                                         | IRQ8-DS      | AN000   | MNET <sup>※1</sup><br>速度設定(0) |

| 94        | VREFL0         |     |                  |                          |                                                         |              |         | GNDに接続                        |

| 96        | VREFH0         |     |                  |                          |                                                         |              |         | VCCに接続                        |

| 97        | AVCC0          |     |                  |                          |                                                         | 1            |         | VCCに接続                        |

| 98        |                | P07 |                  |                          |                                                         | IRQ15        | ADTRG0# | LED(0で点灯)                     |

| 99        | AVSS0          |     |                  |                          |                                                         |              |         | GNDに接続                        |

| 100       |                | P05 |                  |                          |                                                         | IRQ13        | DA1     | 未接続<br>(0を出力)                 |

※ 各ポートの機能設定・ディレクション設定方法に関しては、 「RX63N,RX631 グループ ユーザーズマニュアル ハードウェア編」をご参照下さい。

- ※ 端子名の赤字部は、当該端子に割り当てるべき機能を示しています。

- ※ 未接続のI/O端子は出力に設定し、0を出力して下さい。

- \*1 外部でプルアップされています。

- \*\*2 外部でプルダウンされています。

# 6.5.2. メモリマップ

下表に、LFA7 のメモリマップを示します。

# 表 6 CPU メモリマップ(内蔵 ROM 有効拡張モード)

| アドレス                    | 領域名                       | 容量等   |

|-------------------------|---------------------------|-------|

| H'0000_0000 - 0000_FFFF | 内蔵 RAM                    | 64KB  |

| H'0001_0000 - 0007_FFFF | 予約                        | _     |

| H'0008_0000 - 0009_FFFF | 周辺 I/O レジスタ               | _     |

| H'0010_0000 - 0010_7FFF | 内蔵 E2 データフラッシュ            | 32KB  |

| H'0010_8000 - 007F_7FFF | 予約                        | _     |

| H'007F_8000 - 007F_9FFF | FCU RAM                   | _     |

| H'007F_A000 - 007F_BFFF | 予約                        | _     |

| H'007F_C000 - 007F_C4FF | 周辺 I/O レジスタ               | _     |

| H'007F_C500 - 007F_FBFF | 予約                        | _     |

| H'007F_FC00 - 007F_FFFF | 周辺 I/O レジスタ               | _     |

| H'0080_0000 - 00DF_FFFF | 予約                        | _     |

| H'00E0_0000 - 00FF_FFFF | 内蔵 ROM(書き換え専用)            | _     |

| H'0100_0000 - 08FF_FFFF | 予約                        | _     |

| H'0700_0000 - 0700_01FF | CS1(外部 G9001A アクセス領域)     | _     |

| H'0700_0200 - 07FF_FFFF | 予約                        | _     |

| H'0800_0000-FEFF_DFFF   | 予約                        | _     |

| H'FEFF_E000 - FEFF_FFFF | 内蔵 ROM(FUC ファーム) (読み出し専用) | _     |

| H'FF00_0000 - FF7E_BFFF | 予約                        | _     |

| H'FF7F_C000 - FF7F_FFFF | 内蔵 ROM(ユーザーブート)(読み出し専用)   | _     |

| H'FF80_0000 - FFF9_FFFF | 予約                        | _     |

| H'FFFA_0000 - FFFF_FFFF | 内蔵 ROM(プログラム ROM)(読み出し専用) | 384KB |

<sup>※</sup> 予約領域にはアクセスしないで下さい。(アクセスした場合の動作は保証致しません。)

#### 6.5.3. 動作モードの設定

RX631 には 4 つの動作モードがあり、MD 端子、PC7 端子とソフトウェアで選択します。 S1 は MD 端子、PC7 端子を設定します。 (動作モードの詳細は、「RX63N,RX631 グループ ユーザーズマニュアル ハードウェア編」をご参照下さい。)

表 7 S1による動作モードの選択

| S        | 1         | 動作モード         | SYSCR0 レジスタ設定値 |           |  |

|----------|-----------|---------------|----------------|-----------|--|

| bit1(MD) | bit2(PC7) | <b>到下</b> し一下 | ROME ビット       | EXBE ビット  |  |

| OFF      | OFF       | シングルチップモード    | 1 (内蔵 ROM 有効)  | 1(外部バス有効) |  |

|          | ON        | ブートモード        | としてください。       | としてください。  |  |

| ON       | OFF       | USBブートモード     |                |           |  |

|          | OFF       | ユーザブートモード     |                |           |  |

<sup>※</sup> 出荷時は両 bit ともに「OFF」です。

<sup>※</sup> デバッガによるプログラムの書込み(上表の各ブートモード)やデバッグを行う場合は、別途オプション基板が必要です。

#### 6.5.4. クロック設定

14.7456MHz 水晶発振子接続時最速動作の推奨設定値を下表に示します。

表 8 クロック発生回路設定レジスタ

| レジスタ名  | アドレス        | 推奨設定値        | 設定内容                           |

|--------|-------------|--------------|--------------------------------|

|        |             |              | PCLKB=44.2368MHz,              |

|        |             |              | BCLK=44.2368MHz,               |

| SCKCR  | H'0008_0020 | H' 21C2_1211 | BCLK/SDCLK=出力禁止(Hi 固定),        |

|        |             |              | ICLK=88.4736MHz,               |

|        |             |              | FCLK=44.2368MHz                |

| SCKCR2 | H'0008_0024 | H'0022       | IECLK=44.2368MHz,UCLK=3 分周     |

| SCKCR3 | H'0008_0026 | H'0400       | PLL 回路選択                       |

| PLLCR  | H'0008_0028 | H'0D00       | PLL 入力分周=1,逓倍=×12(176.9472MHz) |

<sup>※</sup> 設定の詳細情報は、「RX63N,RX631 グループ ユーザーズマニュアル ハードウェア編」をご参照 下さい。

#### 6.5.5. 割込み設定

モーションネット制御 LSI(G9001A)からの割込み要求信号は、CPU の IRQ12 に接続されています。 G9001A<->CPU 間で割込みを使用する場合の設定例を下表に示します。

表 9 割込みレジスタの設定例

| レジスタ名   | アドレス        | 推奨設定値 | 設定内容       |

|---------|-------------|-------|------------|

| IEM2    | H'0008_7203 | H'10  | IRQ12割込み許可 |

| IPR12   | H'0008_730C | H'0F  | 割込みレベル=15  |

| IRQCR12 | H'0008_750C | H'04  | 立下りエッジ     |

※ 設定の詳細情報は、「RX63N,RX631 グループ ユーザーズマニュアル ハードウェア編」をご参照 下さい。

#### 7. コマンド・レスポンス仕様

本章では、LFA7と制御装置側間の調歩同期通信部の仕様を記載します。

LFA7 は、制御装置からの調歩同期通信によるコマンド(キャラクタコード)+制御コード (cr(H'13))を受信する事により動作を実行します。

(以降、コマンド出力部の事を総称してコンソールと記載致します。)

また、コマンドの種類・内容は、コンソールから HELP[cr]と入力する事により確認できます。

電源投入、または、リセット操作後のデフォルト通信フォーマットを表 10、コマンド・レスポンス仕様を表 11 に示します。

表 10 デフォルト通信フォーマット

| 設定内容    | 設定値     |

|---------|---------|

| ボーレート   | 9600bps |

| データ長    | 8 bit   |

| パリティ    | none    |

| ストップビット | 1bit    |

| フロー制御   | none    |

# 表 11 コマンド・レスポンス仕様

| コマンド<br>(コンソール→LFA7)                      | レスポンス<br>(LFA7→コンソール)                | 機能                                    | パラメータ・返値説明                                 |  |

|-------------------------------------------|--------------------------------------|---------------------------------------|--------------------------------------------|--|

| ?[cr]                                     | LFA 7[cr]                            | 製品型式返信                                |                                            |  |

| VER[cr]                                   | VER YYYY_MM_DD[cr] <sup>* 1</sup>    | LFA7 のバージョン表示                         |                                            |  |

| RES[cr]                                   | RES[cr]→LFA 7[cr]                    | WDT によるソフトウェアリセット                     |                                            |  |

| SBD n[cr]                                 | Set boreat n[cr]                     | <br>  調歩同期ポートボーレート設定                  | n=ボーレート(300~115200)                        |  |

| SDM c[cr]                                 | SDM c[cr]                            | コンソール入出力デーチモード設定                      | c=H(アスキーHEX),<br>B(BIN モード),<br>D(アスキーDEC) |  |

| SEN c[cr]                                 | SEN c[cr]                            | エンディアン設定                              | c=B(ビッグエンディアン),<br>L(リトルエンディアン)            |  |

| SAM n[cr]                                 | SAM n[cr]                            | アクセスモート*設定                            | n=連続リート*/ライト時のアドレス<br>変化量                  |  |

| SBA n[cr]                                 | SBA n[cr]                            | ベースアドレス設定                             | n=リード/ライト時のベースアドレス                         |  |

| RDB a k[cr]                               | RDB d[cr](指定回数分)                     | 指定アドレスからのバイト(8bit)リード                 | a=アドレス                                     |  |

| RDW a k[cr]                               | RDW d[cr](指定回数分)                     | 指定アドレスからのワード(16bit)リード                | ・k=リードバイト数                                 |  |

| RDL a k[cr]                               | RDL d[cr](指定回数分)                     | 指定アドレスからの<br>ダブルワード(32bit)リード         | d=リードデータ(返値)                               |  |

| WRB a k d[cr]                             | WRB a d[cr](指定回数分)                   | 指定アドレスへのバイト(8bit)ライト                  | <b>—</b> 191 —                             |  |

| WRW a k d[cr]                             | WRW a d[cr](指定回数分)                   | 指定アドレスへのワード(16bit)ライト                 | ・a=アドレス<br>・k=データ数                         |  |

| WRL a k d[cr]                             | WRL a d[cr](指定回数分)                   | 指定アドレスへの<br>ダブルワード(32bit)ライト          | d=データ<br>d=データ                             |  |

| E2ER b[cr]                                | E2ER[cr]                             | CPU 内蔵 EEPROM<br>プ <sup>*</sup> ロック消去 | b=ブロック番号<br>(0000~1023)                    |  |

| E2RD a n[cr]                              | E2RD[cr] Eraseed Blok[cr] **2 d[cr]  | CPU 内蔵 EEPROM<br>データバイト(8bit)リード      | a=アドレス<br>n=リードバイト数<br>d=リードデータ(返値)        |  |

| E2WRD a n[cr] <sup>※3</sup>               | E2WRD[cr] Eraseed Blok[cr] **2 d[cr] | CPU 内蔵 EEPROM<br>データワード(16bit)リード     | 指定バイト読み出し後に<br>>(プロンプト)を返信                 |  |

| E2WR a n[cr] d                            | E2WR a n[cr]                         | CPU 内蔵 EEPROM<br>データバイト(8bit)ライト      | a=アドレス<br>n=ライトバイト数                        |  |

| E2WWR a n[cr] d <sup>※3</sup>             | E2WWR a n[cr]                        | CPU 内蔵 EEPROM<br>データワード(16bit)ライト     | d=ライトデータ<br>指定バイト書き込み後に<br>>(プロンプト)を返信     |  |

| PLW n r d[cr]                             | PLW n r d[cr]                        | Motionnet ローカルデバイス書込み                 | n=デバイス番号                                   |  |

| PLR n r[cr]                               | PLR n r d[cr]                        | Motionnet ローカルデバイス読込み                 | r=ローカルレジスタ<br>d=データ                        |  |

| CT tid dd dd dd dd dd<br>dd dd dd[cr] **3 | CT[cr]                               | Motionnet 送信                          | tid=送信 ID<br>dd=データ(省略可)                   |  |

| コマンド<br>(コンソール→LFA7)                | レスポンス<br>(LFA7→コンソール) | 機能                         | パラメータ・返値説明                                                  |

|-------------------------------------|-----------------------|----------------------------|-------------------------------------------------------------|

| CR mb rid[cr] <sup>**3</sup> CR[cr] |                       | Motionnet 受信設定             | mb=メールボックス<br>rid=受信 ID 値                                   |

| CBS k[cr] **3                       | Motionnet BPS = k[cr] | Motionnet ビットレートセット[kbps]  | k=1000,500,250,125,83,33                                    |

| MotionnetT k[cr] **3                | Motionnet TEST[cr]    | Motionnet 繰り返し送信テスト        | k=間隔(1~10)(msec 単位)<br>(省略時 10msec)                         |

| SC[cr] <sup>※3</sup>                | SC[cr]                | 全メール BOX[0-31]を<br>受信設定にする |                                                             |

| MBD d[cr]                           | MBD d[cr]             | Motionnet 通信速度設定・保存        | d = 02(2.5Mbps)<br>05( 5Mbps)<br>10( 10Mbps)<br>20( 20Mbps) |

| HELP[cr]                            |                       | コマンド一覧が表示されます。             |                                                             |

<sup>\*\*1</sup> YYYY:西暦、MM:月、DD:日を示します。

<sup>※2</sup> アドレス指定されたブロックが消去されていなかった場合にブロック消去処理が入ります。

<sup>\*\*3</sup> 拡張コマンドとなっており非実装です。将来実装予定。 コマンド入力されてもレスポンスの返信はありません。

#### 8. 外部接続仕様

# 8.1. 調歩同期通信部インターフェース

調歩同期通信側装置とは、下図コネクタの何れか (実装オプションでの選択) により RS232C、あるいは、LVTTL レベルインターフェースにより CPU 内蔵 UARTO 機能端子に接続されます。 ※下図 CN3-5、PAD1-9 は、実装オプションでどれか 1 つを選択します。

(詳細は、本書表1をご参照下さい)

図 9 調歩同期インターフェース部接続部

#### 8.1.1. 電気的インターフェースの選択

調歩同期通信の外部との電気的インターフェースは、RS232C と LVTTL の何れかを選択可能となっており、図8の CN5 が LVTTE ポート、他が RS232C 接続用です。

電気的インターフェースの選択は、基板上のHJ1、HJ2により下表の通りとなります。

表 12 調歩同期接続部電気的インターフェース選択

| 外部       | 設     | 定     | 備考                    |

|----------|-------|-------|-----------------------|

| インターフェース | НЈ1   | HJ2   | V⊞*⊃                  |

| RS232C   | 開放開放  |       | オプション指定をされた場合は、当社で設定し |

| LVTTL    | 半田で短絡 | 半田で短絡 | た状態にて出荷されます。          |

<sup>※</sup>HJ1,HJ2 の位置は、本書 T.B.D の部品面部品配置図をご参照下さい。

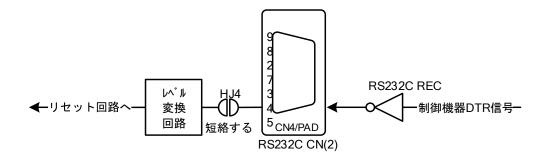

# 8.1.2. RS232C DTR 信号によるリセット処理設定ジャンパ(HJ4)

HJ4 は、外部 RS232C(CN4(4),PAD4)の DTR 接続により LFA7 のリセット信号をアクティブにする機能の有効・無効を設定します。

表 13 HJ4 処理仕様

| НЈМо. | DTR 信号による | 5リセット処理 | - 備考      |  |

|-------|-----------|---------|-----------|--|

|       | 開放時       | 短絡時     | ™°⊃       |  |

| 4     | 行わない 行う   |         | 出荷時は開放です。 |  |

#### 8.1.3. RS232C シリアル通信信号接続コネクタ 1(CN3)

CN3 は、ナイロンコネクタ、または、ピンヘッダ実装用部で、CPU 内蔵 UARTO 機能端子 に RS232C ドライバを介し接続されています。

尚 RS232C インターフェースにて通信を行いたい場合は、基板上の **HJ1,HJ2 は開放** とし、RS232C ドライバを有効とする必要があります。

(実装をご希望される場合は、ご発注時に本書表 1 オプション番号①で T.B.D の何れかの番号をご指定下さい。)

表 14 RS232C シリアル通信信号接続コネクタピンアサイン(CN3)

| 端子番号 | 信号名   | 入出力 | 内容              | 電気的 I/F     |

|------|-------|-----|-----------------|-------------|

| 1    | R_TXD | I   | シリアル送信データ       | RS-232C     |

| 2    | R_RTS | I   | 送信許可信号          | RS-232C     |

| 3    | R_RXD | 0   | シリアル受信データ       | RS-232C     |

| 4    | R_CTS | 0   | 送信要求信号          | RS-232C     |

| 5    | GND   | PI  | LFA7 電源         | 0V          |

| 6    | VCC   | PI  | LFA7 電源         | +5VDC       |

| 7    | nRES  | I   | リセット(オーフ°ンコレクタ) | 0V~+3.3VDCC |

表 15 CN3 実装コネクタ選択仕様

| オプション<br>番号① | 実装品             | 適合ソケット          | コンタクト            | メーカー   |

|--------------|-----------------|-----------------|------------------|--------|

| 1            | IL-G-6P-S3T2-SA | IL-G-6S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

| 3            | IL-G-7P-S3T2-SA | IL-G-7S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

| 5            | XR2P-0641       | XR2C-0611-N 等   | _                | オムロン   |

| 8            | XR2P-0741       | XR2C-0711-N 等   | _                | オムロン   |

<sup>※</sup>オプション番号の詳細は、本書表 1、及び、1.2.1 項をご参照下さい。

<sup>※</sup>ソケット・コンタクトはお客様でご用意下さい。

#### 8.1.4. RS232C シリアル通信信号接続コネクタ 2(CN4)

CN4 は、D\_SUB 9P オスコネクタ実装部で、CPU 内蔵 UARTO 機能端子に RS232C ドライバを介し接続されています。

尚 RS232C インターフェースにて通信を行う場合は、基板上の **HJ1,HJ2 は開放** とし、RS232C ドライバを有効とする必要があります。

(実装をご希望される場合は、ご発注時に本書表 1 オプション番号①で 7 をご指定下さい。)

#### 表 16 RS232C シリアル通信信号接続コネクタピンアサイン 2(CN4)

使用コネクタ: CD5309PA100(シビラックス)または同等品

適合ソケット: CD9S2100(シビラックス)または同等品

| 端子番号 | 信号名                 | 入出力 | 内容        | 電気的 I/F | 外形        |

|------|---------------------|-----|-----------|---------|-----------|

| 1    | NC                  | _   | 未接続       | _       |           |

| 2    | R_RXD               | I   | シリアル受信データ | RS-232C |           |

| 3    | R_TXD               | 0   | シリアル送信データ | RS-232C |           |

| 4    | R_DTR               | I   | リセット      | RS-232C | 1 2 3 4 5 |

| 5    | GND                 | PI  | LFA7 電源   | 0V      |           |

| 6    | NC                  | _   | 未接続       | _       | 6 7 8 9   |

| 7    | R_RTS               | 0   | 送信要求信号    | RS-232C |           |

| 8    | R_CTS               | I   | 送信許可信号    | RS-232C |           |

| 9    | +5V <sup>** 1</sup> | PI  | LFA7 電源   | +5VDC   |           |

<sup>※1</sup>本端子から電源を給電する場合は、HJ6 を短絡する必要があります。

#### 8.1.5. RS232C シリアル通信信号接続コネクタ 3(PAD1-9)

PAD1-9 は、D\_SUB 9P メスケーブル半田付けタイプコネクタ実装部で、CPU 内蔵 UARTO 機能端子に RS232C ドライバを介し接続されています。

尚 RS232C インターフェースにて通信を行う場合は、基板上の **HJ1,HJ2 は開放**とし、RS232C ドライバを有効とする必要があります。

(実装をご希望される場合は、ご発注時に本書表1オプション番号①で6をご指定下さい。)

#### 表 17 RS232C シリアル通信信号接続コネクタピンアサイン 3(PAD1-9)

使用コネクタ: CD5109SA100-E (シビラックス)または同等品 適合ソケット: CD519PPA100-E (シビラックス)または同等品

|        |                    | •   | •         |         |           |

|--------|--------------------|-----|-----------|---------|-----------|

| PAD 番号 | 信号名                | 入出力 | 内容        | 電気的 I/F | 外形        |

| 1      | NC                 | _   | 未接続       | -       |           |

| 2      | R_TXD              | 0   | シリアル送信データ | RS-232C |           |

| 3      | R_RXD              | I   | シリアル受信データ | RS-232C | 5 4 0 0 4 |

| 4      | R_DTR              | I   | リセット      | RS-232C | 5 4 3 2 1 |

| 5      | GND                | PI  | LFA7 電源   | 0V      |           |

| 6      | NC                 | _   | 未接続       | _       | 9876      |

| 7      | R_CTS              | I   | 送信許可信号    | RS-232C |           |

| 8      | R_RTS              | 0   | 送信要求信号    | RS-232C |           |

| 9      | +5V <sup>*</sup> 1 | PI  | LFA7 電源   | +5VDC   |           |

<sup>※</sup>お客様でコネクタを取付ける場合は、コネクタをあまり奥まで押し込まないで下さい。

あまり奥に押し込みますと、信号スルーホールとコネクタの端子がショートし正常に通信できなく なる場合があります。

図 10 PAD1-9 配置図

半田面視

<sup>※1</sup>本端子から電源を給電する場合は、HJ6 を短絡する必要があります。

#### 8.1.6. LVTTL シリアル通信信号接続コネクタ(CN5)

CN5 は、ナイロンコネクタ、または、ピンヘッダ実装部で、CPU 内蔵 UARTO 機能端子が接続されています。

尚 LVTTLインターフェースにて通信を行いたい場合は、基板上のHJ1,HJ2を半田で短絡し、RS232C ドライバを無効とする必要があります。

(実装をご希望される場合は、ご発注時に本書表 1 オプション番号①で表 16 の何れかの番号をご指定下さい。)

表 18 LVTTL シリアル通信信号接続コネクタピンアサイン(CN5)

| 端子番号 | 信号名   | 入出力 | 内容              | 電気的 I/F    |

|------|-------|-----|-----------------|------------|

| 1    | R_TXD | I   | シリアル送信データ       | LVTTL      |

| 2    | R_RTS | I   | 送信許可信号          | LVTTL      |

| 3    | R_RXD | 0   | シリアル受信データ       | LVTTL      |

| 4    | R_CTS | 0   | 送信要求信号          | LVTTL      |

| 5    | GND   | PI  | LFA7 電源         | 0V         |

| 6    | VCC   | PI  | LFA7 電源         | +5VDC      |

| 7    | nRES  | I   | リセット(オーフ°ンコレクタ) | 0V~+3.3VDC |

表 19 CN5 実装コネクタ選択仕様

| オプション<br>番号① | 実装品             | 適合ソケット          | コンタクト            | メーカー   |

|--------------|-----------------|-----------------|------------------|--------|

| 2            | IL-G-6P-S3T2-SA | IL-G-6S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

| 4            | IL-G-7P-S3T2-SA | IL-G-7S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

| 9            | XR2P-0641       | XR2C-0611-N 等   | _                | オムロン   |

| 10           | XR2P-0741       | XR2C-0711-N 等   | _                | オムロン   |

<sup>※</sup>オプション番号の詳細は、本書表 1、及び、1.2.1 項をご参照下さい。

<sup>※</sup>ソケット・コンタクトはお客様でご用意下さい。

#### 8.2. モーションネット制御部接続仕様

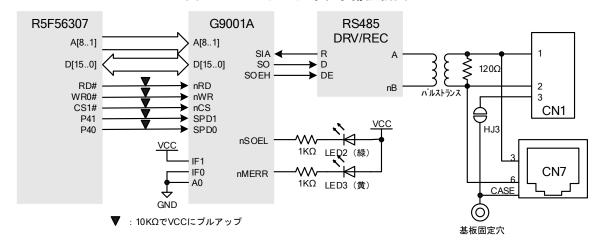

モーションネット接続部は、下図接続となっています。

図 11 モーションネット部接続図

#### 8.2.1. CN1 シールド処理設定ジャンパ(HJ3)

HJ3 は、ケーブルシールドをボード取付け穴に接続するか否かを設定します。

表 20 HJ3 処理仕様

| HJNo. | シールド部 | B接続状態 | 備考        |

|-------|-------|-------|-----------|

|       | 開放時   | 短絡時   | VR1°⊃     |

| 3     | 未接続   | 接続    | 出荷時は開放です。 |

#### 8.2.2. モーションネット接続コネクタ 1(CN1)

本コネクタは 3P ライトアングルのナイロンコネクタで、本書表 1 ③にて 2 を選択された場合に 実装されます。

#### 表 21 モーションネット接続コネクタ 1 ピンアサイン (CN1)

実装コネクタ: DF1B-3P-2.5DS(01)(ヒロセ)

適合ソケット: DF1B-3S-2.5R(01)、コンタクト: DF1B-R28×3 個(ヒロセ)

※専用ケーブルが日本パルスモーター社より販売されています。

| 端子番号 | 信号名       | 入出力 | 内容               | 外形    | 備考        |

|------|-----------|-----|------------------|-------|-----------|

| 1    | DATA A(+) | I/O | Motionnet LINE+  |       | ※左図は、コネクタ |

| 2    | DATA B(-) | I/O | Motionnet LINE – |       | 差込方向から見た図 |

| 3    | *         | -   | ケーブルシールド         | 1 2 3 | です。       |

※ 出荷時はどこにも接続されていません。HJ3 を半田ジャンパすると近接するビス穴の非レジスト部分に接続されます。

#### 8.2.3. モーションネット接続コネクタ 2(CN7)

本コネクタは RJ45 型ライトアングルコネクタで、本書表1③にて 3 を選択された場合に 実装されます。

#### 表 22 モーションネット接続コネクタ 2 ピンアサイン (CN7)

実装コネクタ: TM24RSG-5A-88(ヒロセ)

適合ソケット TM20P-88P 等(ヒロセ等)

※EtherNET (CAT5 以上)ケーブルでの接続を推奨致します。

| 端子番号 | 信号名       | 入出力 | 内容               | 外形                       | 備考                                     |

|------|-----------|-----|------------------|--------------------------|----------------------------------------|

| 1    | NC        | 1   | 非接続              |                          |                                        |

| 2    | NC        | -   | 非接続              | r√j <del>i</del> ==t√n   |                                        |

| 3    | DATA A(-) | I/O | Motionnet LINE+  |                          | ************************************** |

| 4    | NC        | _   | 非接続              | ▎┸ <b>╠╟╫╫╫╫</b> ╢╣┸     | ※左図は、コネクタ<br>差込方向から見た図                 |

| 5    | NC        | _   | 非接続              | ╽┰╚╧┇┇┇                  | <u> </u>                               |

| 6    | DATA B(-) | I/O | Motionnet LINE – | <b>(1</b> 11 pynnpy 111) | C 7 °                                  |

| 7    | NC        | _   | 非接続              | 8 1                      |                                        |

| 8    | NC        | _   | 非接続              |                          |                                        |

# 8.2.4. CPU と LSI(G9001A)の接続

モーションネット制御 LSI(G9001A)と CPU は下表・下図の接続となっています。

表 23 G9001A<->CPU 信号接続仕様

| G9001A側 |     |                       | CPU側    |     |              |         |                     |  |

|---------|-----|-----------------------|---------|-----|--------------|---------|---------------------|--|

| 端子名     | PIN | 信号の方向                 | PIN 端子名 |     |              | 機能・接続   |                     |  |

|         | NO  |                       | NO      | I/O | BUS          | 割込み     |                     |  |

| nWRQ    | 38  | $\rightarrow$         | 39      | P55 | WAIT#        | IRQ10   | G9001A→CPUへのWAIT要求  |  |

| nRD     | 5   | <b>←</b>              | 42      | P52 | RD#          |         | CPU→G9001Aへのリード要求   |  |

| nWR     | 4   | <b>←</b>              | 44      | P50 | WR0#/WR#     |         | CPU→G9001Aへのライト要求   |  |

| nCS     | 3   | <b>←</b>              | 46      | PC6 | A22/CS1#     | IRQ13   | CPU→G9001Aへのチップセレクト |  |

| nINT    | 37  | $\rightarrow$         | 51      | PC1 | A17          | IRQ12   | G9001A→CPUへの割込み要求   |  |

| A8      | 15  | <b>←</b>              | 61      | PB0 | A8           | IRQ12   | CPU→G9001Aへのアドレス8   |  |

| A7      | 14  | <b>←</b>              | 63      | PA7 | A7           |         | CPU→G9001Aへのアドレス7   |  |

| A6      | 13  | <b>←</b>              | 64      | PA6 | A6           |         | CPU→G9001Aへのアドレス6   |  |

| A5      | 12  | <b>←</b>              | 65      | PA5 | A5           |         | CPU→G9001Aへのアドレス5   |  |

| A4      | 11  | <b>←</b>              | 66      | PA4 | A4           | IRQ5-DS | CPU→G9001Aへのアドレス4   |  |

| А3      | 9   | <b>←</b>              | 67      | PA3 | A3           | IRQ6-DS | CPU→G9001Aへのアドレス3   |  |

| A2      | 8   | <b>←</b>              | 68      | PA2 | A2           |         | CPU→G9001Aへのアドレス2   |  |

| A1      | 7   | <b>←</b>              | 69      | PA1 | A1           | IRQ11   | CPU→G9001Aへのアドレス1   |  |

| D15     | 35  | $\longleftrightarrow$ | 71      | PE7 | D15[A15/D15] | IRQ7    | CPU←→G9001A間データ15   |  |

| D14     | 34  | $\longleftrightarrow$ | 72      | PE6 | D14[A14/D14] | IRQ6    | CPU←→G9001A間データ14   |  |

| D13     | 33  | $\longleftrightarrow$ | 73      | PE5 | D13[A13/D13] | IRQ5    | CPU←→G9001A間データ13   |  |

| D12     | 32  | $\longleftrightarrow$ | 74      | PE4 | D12[A12/D12] |         | CPU←→G9001A間データ12   |  |

| D11     | 30  | $\longleftrightarrow$ | 75      | PE3 | D11[A11/D11] |         | CPU←→G9001A間データ11   |  |

| D10     | 29  | $\longleftrightarrow$ | 76      | PE2 | D10[A10/D10] | IRQ7-DS | CPU←→G9001A間データ10   |  |

| D9      | 28  | $\longleftrightarrow$ | 77      | PE1 | D9[A9/D9]    |         | CPU←→G9001A間データ9    |  |

| D8      | 27  | $\longleftrightarrow$ | 78      | PE0 | D8[A8/D8]    |         | CPU←→G9001A間データ8    |  |

| D7      | 25  | $\longleftrightarrow$ | 79      | PD7 | D7[A7/D7]    | IRQ7    | CPU←→G9001A間データ7    |  |

| D6      | 24  | $\longleftrightarrow$ | 80      | PD6 | D6[A6/D6]    | IRQ6    | CPU←→G9001A間データ6    |  |

| D5      | 23  | $\longleftrightarrow$ | 81      | PD5 | D5[A5/D5]    | IRQ5    | CPU←→G9001A間データ5    |  |

| D4      | 22  | $\longleftrightarrow$ | 82      | PD4 | D4[A4/D4]    | IRQ4    | CPU←→G9001A間データ4    |  |

| D3      | 20  | $\longleftrightarrow$ | 83      | PD3 | D3[A3/D3]    | IRQ3    | CPU←→G9001A間データ3    |  |

| D2      | 19  | $\longleftrightarrow$ | 84      | PD2 | D2[A2/D2]    | IRQ2    | CPU←→G9001A間データ2    |  |

| D1      | 18  | $\longleftrightarrow$ | 85      | PD1 | D1[A1/D1]    | IRQ1    | CPU←→G9001A間データ1    |  |

| D0      | 17  | $\longleftrightarrow$ | 86      | PD0 | D0[A0/D0]    | IRQ0    | CPU←→G9001A間データ0    |  |

| SPD1    | 50  | <b>←</b>              | 93      | P41 |              | IRQ9-DS | CPU→G9001AへのSPD1制御  |  |

| SPD0    | 49  | <b>←</b>              | 95      | P40 |              | IRQ8-DS | CPU→G9001AへのSPD0制御  |  |

<sup>※</sup> 端子名の赤字部は、CPUが当該端子に割り当てるべき機能を示しています。

#### 8.2.5. モーションネット制御 LSI(G9001A)の設定端子

#### 1) 接続 CPU 選択端子

G9001A の機能として、接続する CPU を選択できる機能があります。 LFA7 では、下表の値で固定されています。

表 24 G9001A 固定設定端子設定仕様

| 設定項目         | ピン設定         | 設定内容              |  |

|--------------|--------------|-------------------|--|

| CPU-IF モード選択 | IF0=L, IF1=H | I/Fモード3 (8086モード) |  |

#### 2) CPU による端子設定部

G9001A のモーションネット側の通信速度設定端子は、CPU の I/O 端子により下表の設定が可能です。

表 25 G9001A 設定端子の CPU 端子割付仕様

| 通信速度(Mbps) | 設定         |           |  |  |

|------------|------------|-----------|--|--|

| 世后还及(MDps) | P40 (SPD0) | P41(SPD1) |  |  |

| 2.5        | 0          | 0         |  |  |

| 5          | 1          | 0         |  |  |

| 10         | 0          | 1         |  |  |

| 20         | 1          | 1         |  |  |

<sup>※</sup> P40,P41 は CPU、() 内は G9001A の端子名です。

<sup>※</sup> 両端子はプルアップされています。

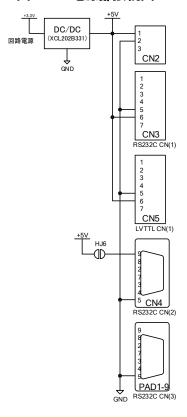

#### 8.3. 電源接続部

LFA7 は、電源受電コネクタ(CN2)、または、CN4・PAD4 からの電源(+5V)により動作します。 また、CN2 の3 番ピンは LFA7 リセット信号に接続されており、外部スイッチ、または、オープンコレクタ信号により LFA7 をリセットする事が可能です。

尚 本コネクタは実装オプションとなっておりますので、実装をご希望される場合は、ご発注時に本書表 1 オプション番号②に表 T.B.D の何れかの番号をご指定下さい。

|  | 端子番号 | 子番号  信号名 |   | 内容              | 電気的 I/F    |  |  |

|--|------|----------|---|-----------------|------------|--|--|

|  | 1    | +5V      | Р | LFA7 電源         | +5VDC      |  |  |

|  | 2    | GND      | Р | LFA7 電源         | 0V         |  |  |

|  | 3    | nRES     | I | リセット(オーフ°ンコレクタ) | 0V∼+3.3VDC |  |  |

表 26 電源受電コネクタ(CN2)ピンアサイン

表 27 CN2 実装コネクタ選択仕様

| オプション<br>番号② | 実装品             | 適合ソケット          | コンタクト            | メーカー   |

|--------------|-----------------|-----------------|------------------|--------|

| 1            | IL-G-2P-S3T2-SA | IL-G-2S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

| 2            | IL-G-3P-S3T2-SA | IL-G-3S-S3C2-SA | IL-G-C2-SC-10000 | 日本航空電子 |

<sup>※</sup>オプション番号の詳細は、本書表 1、及び、1.2.2 項をご参照下さい。

※ソケット・コンタクトはお客様でご用意下さい。

図 12 電源部接続図

# 8.4. CPU デバッグ・プログラム書込み用コネクタ(CN6)

CN6 には、CPU の JTAG 信号・調歩同期シリアル通信信号・USB 通信信号・電源が接続されています。

CN6 へ別売の基板を接続する事により、弊社開発環境 (YIDE) や E1 エミュレーターを接続し、デバッグや CPU へのプログラム書込みが行える他、USB インターフェースを拡張できます。

#### 表 28 CPUデバッグ・プログラム書込みコネクタ(CN6)

使用コネクタ: DF12D(5.0)-20DP-0.5V(81) (ヒロセ) 適合コネクタ: DF12B-20DS-0.5V (86) (ヒロセ)

| 端子番号 | 信号名       | 入出力 | 内容                                | 外形                                     |

|------|-----------|-----|-----------------------------------|----------------------------------------|

| 1    | TCK       | I   | データ同期信号                           |                                        |

| 2    | GND       | Р   | GND                               |                                        |

| 3    | nTRST     | I   | リセット要求                            |                                        |

| 4    | EMLE      | I   | オンチップ° エミュレータイネーフ゛ル <sup>※1</sup> |                                        |

| 5    | TDO       | 0   | シリアルデータ出力信号                       |                                        |

| 6    | NC        | _   | 未接続                               |                                        |

| 7    | MD        | I   | CPU 動作-ド設定 <sup>※1※2</sup>        |                                        |

| 8    | VCC       | Р   | +3.3V 電源                          | 0 6                                    |

| 9    | TMS       | I   | 元パモート"選択信号                        |                                        |

| 10   | PC7       | I   | CPU ブートモード設定 <sup>※1※2</sup>      | -0000000000000000000000000000000000000 |

| 11   | TDI       | I   | 刘別后"-9入力信号                        |                                        |

| 12   | GND       | Р   | GND                               |                                        |

| 13   | nRES      | I   | CPU リセット                          |                                        |

| 14   | GND       | Р   | GND                               |                                        |

| 15   | VBUS      | Р   | USB 電原                            |                                        |

| 16   | VBUS      | Р   | USB 電原                            |                                        |

| 17   | nUSB_DM   | I/O | USB 送受信-                          |                                        |

| 18   | USB_DP    | I/O | USB 送受信+                          |                                        |

| 19   | USB_DPUPE | 0   | USB 外部でパプップ。制御                    |                                        |

| 20   | GND       | Р   | GND                               |                                        |

<sup>\*\*2</sup> S1にも接続されています。

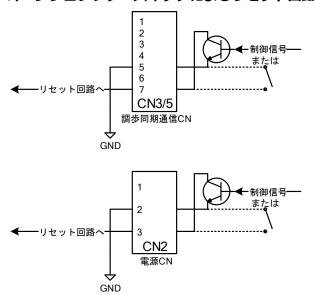

#### 8.5. 外部からのボードリセット操作

LFA7 には、電源 ON 時のリセット以外に LFA7 上の CPU が動作不能状態となったとき等に、オープンコレクタ、または、RS232C の DTR 信号入力による外部リセットを行う機能を設けています。

#### 8.5.1. オープンコレクタ・スイッチによるリセット操作

CN3,CN5の7番端子、および、CN2の3番端子の基板内リセット信号配線に直接接続されています。本リセット接続をご使用される場合は、下図接続としてください。

図 13 オープンコレクタ・スイッチによるリセット回路接続図

#### 8.5.2. RS232C DTR 信号によるリセット操作

CN4の4番端子、または、PAD4はHJ4、レベル変換回路を経て基板内リセット信号配線に接接続されています。

図 14 RS232C DTR 信号接続図

#### 9. インジケーター部

本基板部品面には、以下の LED が実装されています。

# 9.1.1. CPU 制御 LED(LED1)

CPU で制御可能な橙色の LED です。

本 LED を制御する場合は、CPU の P07 ポートを出力に設定する必要があります。

(プリインストールプログラム実行時は、500ms の点滅動作となります。)

表 29 CPU 制御 LED 制御仕様

| CPU 制御ポート | 制御方法    |         |  |

|-----------|---------|---------|--|

|           | ON(点灯)  | OFF(消灯) |  |

| P07       | '0'をライト | '1'をライト |  |

# 9.1.2. モーションネットステータス LED(LED2,3)

Motionnet 通信部のステータスを示す LED で、G9001A のステータス出力端子に接続されています。

表 30 G9001A 制御 LED 制御仕様

| G9001A | ロケーション | 色 | 表示内容    |         |

|--------|--------|---|---------|---------|

| 接続端子名  |        |   | ON(点灯)  | OFF(消灯) |

| nSOEL  | LED2   | 緑 | 通信実行中   | 通信未実行   |

| nMERR  | LED3   | 黄 | 通信エラー発生 | 通信正業    |

#### 変更履歴

# 変更箇所には直前の版との相違を表示するマーク「☆」があります。

| 版   | 変更理由         | 変更ページ 変更事項               | 変更日        |

|-----|--------------|--------------------------|------------|

| 1.0 |              | 新規作成                     | 2016/03/30 |

| 1.1 | コマンドの追加・一部修正 | P22~P24                  |            |

|     |              | 7.コマンド・レスポンス仕様(T.B.D)    | 2018/07/31 |

|     |              | 表 11.コマンド・レスポンス仕様        |            |

|     |              | P25 表 14 CN4 ピンアサイン「入出力」 |            |

| 1.2 | 誤記修正         | の行Iと0の関係を反転              | 2010/0E/21 |

| 1.2 | 最高)多正<br>    | P28 表 18 CN5 ピンアサイン「入出力」 | 2019/05/21 |

|     |              | の行Iと0の関係を反転              |            |

| 1.3 | 誤記修正         | P27 表 17 ピンアサインを全面修正     | 2022/10/31 |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

|     |              |                          |            |

- ◆ 本文書に記載した内容は、慎重に製作致しましたが、万一、ご不審点、誤り等お気付き の点がございましたらご連絡いただきたくお願い致します。

- ◆ 本書に記載されているブランド名または製品名は、それらの所有者の商標もしくは登録 商標です。

- 本取扱い説明書の閲覧には、Adobe 社の AcrobatReader が必要です。

- 製品に関するお問合せは、回答の正確性を維持する意味において下記 e-mail、または、FAX でのみ受け付けております。

電話にてのお問合せは受け付けておりませんのでご了承下さい。

# 株式会社エル・アンド・エフ 〒175-0083

# 東京都板橋区徳丸4-2-9

URL: https://www.l-and-f.co.jp

FAX: 03-5398-1181

E-mail: toiawase@l-and-f.co.jp